|

|

|

Le bus PCI (Peripheral Component Interconnect) a été mis au point par Intel le 22 juin 1992. Contrairement au bus VLB il ne s'agit pas à proprement parler d'un bus local mais d'un bus intermédiaire situé entre le bus processeur (NorthBridge) et le bus d'entrées-sorties (SouthBridge).

Les connecteurs PCI sont généralement présents sur les cartes mères au nombre de 3 ou 4 au minimum et sont en général reconnaissables par leur couleur blanche (normalisée). L'interface PCI existe en 32 bits, avec un connecteur de 124 broches, ou en 64 bits, avec un connecteur de 188 broches. Il existe également deux niveaux de signalisation :

Il existe 2 types de connecteurs 32 bits :

Les connecteurs PCI 64 bits proposent des broches supplémentaires, mais peuvent néanmoins accueillir les cartes PCI 32 bits. Il existe 2 types de connecteurs 64 bits :

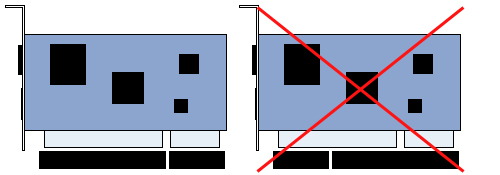

D'une manière générale, il n'est pas possible de se tromper lors du branchement d'une carte PCI dans un emplacement PCI. En effet, dans la mesure où la carte s'enfiche correctement, elle est compatible, dans le cas contraire des détrompeurs empêcheront son installation.

Il existe des cartes d'extension possédant des connecteurs dits « universels « (en anglais universal), c'est-à-dire possédant les deux types de détrompeurs (deux encoches). Ces cartes d'extension sont capables de détecter la tension de signalisation et de s'y adapter et peuvent ainsi être insérées indépendamment dans des emplacements 3.3 V ou 5 V.

Le bus PCI, dans sa version initiale, possède une largeur de 32 bits et est cadencé à 33 MHz ce qui lui permet d'offrir un débit théorique de 132 Mo/s en 32 bits. Sur les architectures 64 bits le bus fonctionne à 64 bits et propose un taux de transfert théorique de 264 Mo/s Un groupement d'intérêt constitué d'un grand nombre de constructeurs, baptisé PCI-SIG (PCI Special Interests Group), a vu le jour afin de faire évoluer le standard PCI. Des révisions du bus ont ainsi été publiées. La version 2.0 du 30 avril 1993 définit la géométrie des connecteurs et des cartes additionnelles et lui permet d'être cadencé à 66 MHz, contre 33 MHz pour la version 1.0, et double ainsi son taux de transfert théorique, pour atteindre 266 Mo/s en 32 bits. Le 1er juin 1995, la révision 2.1 du bus PCI améliore son utilisation à 66 MHz. Les ingénieurs prévoient à cette époque une évolution progressive de la tension de signalisation de 5 V vers une signalisation en 3.3 V. La version 2.2 du bus PCI, parue le 18 décembre 1998, permet le branchement à chaud des périphériques (hot plug). La révision 2.3, éditée le 29 mars 2002, supprime la possibilité d'utiliser des cartes additionnelles 5V, mais gard la possibilité d'utiliser des cartes supportant les deux tensions pour assurer une compatibilité descendante. La révision 3.0 du standard PCI supprime toute possibilité d'utiliser des cartes compatibles 5V. En septembre 1999, une évolution majeure du bus PCI voit le jour, baptisée PCI-X. Le bus PCI-X 1.0 supporte des fréquences de 66, 100 et 133 MHz. Le bus PCI-X est pleinement compatible avec le format PCI et permet ainsi d'utiliser des cartes additionnelles au format PCI conventionnel dans des emplacements PCI-X et vice-versa. La révision 2.0 du bus PCI-X supporte des fréquence de 66, 100, 133, 266 et 533 MHz et permet d'atteindre des débits de l'ordre de 4.27 Go/s en 64 bits. Le tableau ci-dessous récapitule les différentes révisions du bus PCI :

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Ce document intitulé « Ordinateur - Le bus PCI » issu de Comment Ça Marche est mis à disposition sous les termes de la licence Creative Commons. Vous pouvez copier, modifier des copies de cette page, dans les conditions fixées par la licence, tant que cette note apparaît clairement. |